February 23, 2014

To: Dr. David Michelson

From: Danny Kim, L2C4 Team Leader

This memorandum serves as an update for progress of the EECE 380 Design Studio III team, L2C4, during the week of February 17 – February 23, 2014.

We had our weekly team meeting on Monday, February 17, where we talked about our progress in the software and hardware portions of the project from the previous week.

Updates on Hardware Portion:

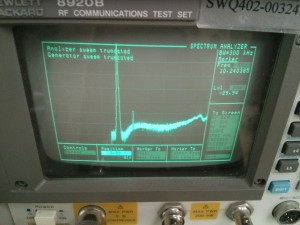

The 4 pole crystal ladder filter we previously designed did not have enough gain from its resolution peak from the noise of the circuit as we hoped. We decided to improve our design by building a 2 pole crystal ladder filter with a better gain. With our original filter having ~1 KHz bandwidth, our new filter has a bandwidth of ~2 KHz in order for us to see how high the peak of a signal is. Previously, the signal was getting attenuated but as a result of our improved crystal ladder filter, at our centre frequency, we are getting a gain of ~10 dBm when the Mixer, Voltage Controlled Oscillator, and RF Amplifier are all connected.

We were having trouble with the output of the crystal ladder filter being too low of a voltage to be accurately measured by the peak detector. We decided to add an amplifier after the filter and before the detector. We designed two different solutions. The first is a CE-CB cascode amplifier that creates isolation from the input to the output and the second is a 4th order butterworth low pass filter using 2 high speed amplifiers. The butterworth was able to pass a signal through with much less distortion and we were able to create a voltage gain of up to 100V/V. We are unsure of which one to use as of now. The butterworth is a much better amplifier, but it comes with the cost of a much more complex circuit.

We spent this week solely on hardware, so there is no update from software portion this week.

In the following week, we plan on meeting on February 24th to discuss current state of the project and plan our goals.